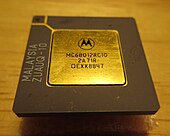

Motorola 68010

| General information | |

|---|---|

| Launched | 1982 |

| Designed by | Motorola |

| Performance | |

| Max. CPU clock rate | 8 MHz to 16.67 MHz |

| Data width | 16 bits |

| Address width | MC68010: 24 bits MC68012: 31 bits |

| Architecture and classification | |

| Instruction set | Motorola 68000 series |

| Physical specifications | |

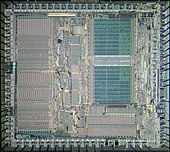

| Transistors |

|

| Packages | |

| History | |

| Predecessor | Motorola 68000 |

| Successor | Motorola 68020 |

The Motorola MC68010 and Motorola MC68012 are 16/32-bit microprocessors from Motorola, released in 1982 as successors to the Motorola 68000.[3] The 68010 and 68012 added virtualization features, optimized loops and fixed several small flaws to the 68000. The MC68010 variants were pin compatible with its predecessor while the MC68012 is an 84-pin PGA version with its directly accessible memory space extended to 2 GiB.[2][4]

Differences between 68010/68012 and 68000

The 68010 and 68012 are completely user-mode compatible with the 68000, except that the MOVE from SR instruction traps in user mode, so that, to support user-mode code using that instruction, a supervisor-mode trap handler must simulate the instruction and continue the user-mode code after that instruction. This was done so that the 68010 and 68012 would meet the Popek and Goldberg virtualization requirements, specifically that a new OS could run as guest and not be aware.[2]: §1.3.2 A new unprivileged MOVE from CCR instruction was added to compensate for the penalty of trapping user-mode MOVE from SR.

The 68010 and 68012 can recover from bus faults, and continue the faulting instruction, allowing them to implement virtual memory. This means that the exception stack frame is different.

A 32-bit Vector Base Register (VBR) holds the base address for the exception vector table. The 68000 vector table was always based at address zero.

A "loop mode" accelerates loops consisting of only a "loopable" instruction and a DBcc (Decrement/Branch on condition); an example would be MOVE and DBRA. The two-instruction mini-loop opcodes are prefetched and held in the 6-byte instruction cache while subsequent memory read/write cycles are only needed for the data operands for the duration of the loop.[2]: §7.1.3 It provided for performance improvements averaging 50%, as a result of the elimination of instruction opcodes fetching during the loop.

The MC68012 variant, in addition to its memory space being extended to 2 GiB, also added a read-modify-write cycle (RMC) pin, indicating that an indivisible read-modify-write cycle in progress, in order to help the design of multiprocessor systems with virtual memory.

The expansion of the memory space in the 68012 caused an issue for any programs that used the high byte of an address to store data, a programming trick that was successful with those processors that only have a 24-bit address bus (68000 and 68010). A similar problem affected the 68020.

Usage

The 68010 was never as popular as the 68000. However, due to the 68010's small speed boost over the 68000 and its support for virtual memory, it can be found in a number of smaller Unix systems, both with the 68451 MMU (for example in the Torch Triple X), and with a custom MMU (such as the Sun-2 Workstation, AT&T UNIX PC/3B1, Convergent Technologies MiniFrame, Plexus P/15 and P/20,[5] NCR Tower XP, Apollo Computer's DN300 and DN320,[6] and HP 9000 Model 310) and various research machines. Most other vendors (such as Apple Computer) stayed with the 68000 until the 68020 was introduced.

Atari Games used the 68010 in some of their arcade boards such as the Atari System 1. Some owners of Amiga and Atari ST computers and Sega Genesis game consoles replaced their system's 68000 CPU with a 68010 to gain a small speed boost.[7]

In practice, the overall speed gain over a 68000 at the same frequency is less than 10%.

The 68010 could be used with the 68451 MMU. However, aspects of its design, such as its 1 clock memory access penalty, made this configuration unpopular. Some vendors used their own MMU designs, such as Sun Microsystems in their Sun-2 workstation and Convergent Technologies in the AT&T UNIX PC/3B1.

References

- ^ "i486, 68040 Use Pipelining To Speed Up Performance". InfoWorld: 39. May 8, 1989.

- ^ a b c d e f g MC68010/MC68012 16-/32-Bit Virtual Memory Microprocessors (PDF). Motorola Semiconductor. May 1985. Archived (PDF) from the original on 2020-03-28.

- ^ "Motorola 68010 (MC68010) family". CPU World.

- ^ Avtar, Singh; Triebel, Walter A. (1991). 16-Bit and 32-Bit Microprocessors: Architecture, Software, and Interfacing Techniques. Englewood Cliffs, New Jersey: Prentice-Hall. ISBN 978-0138121570.

- ^ "Plexus P/15-P/20 Brochure" (PDF). UserManual.wiki. Plexus Computers, Inc. 1985. Retrieved 2024-05-28.

- ^ "Apollo Computer Technical Publications Overview" (PDF). Apollo Computer. June 1987. Retrieved 2022-10-13.

- ^ Floryan, Thad. "AMIGA (tm) TECHNICAL NOTE Upgrading an AMIGA A1000 with a Motorola MC68010L8".